使用Clock Builder Pro的晶體振蕩器實現最佳抖動性能放置向導

當高頻晶體振蕩器信號彼此接近時,另外,串擾很可能會影響抖動每個輸出的性能.了解如何放置輸出時鐘Si538x/4石英晶體振蕩器上的引腳可實現最佳抖動和串擾性能.本應用筆記提供了Clock Builder Pro的“時鐘放置向導”概述以及如何使用它來為您的頻率計劃和設備配置獲得最佳的抖動和串擾性能.

1.晶體振蕩器最低抖動和串擾的設計準則

在介紹“時鐘晶體振蕩器放置向導”如何工作以及如何使用它來實現特定有源晶體振蕩器的最低抖動和串擾之前,Si538x/4x頻率計劃,請考慮以下輸出時鐘引腳配置準則.

1.1盡可能使用差分輸出格式

為了獲得最佳性能,強烈建議使用差分輸出格式,例如LVDS,LVPECL,CML或HCSL.雖然晶體振蕩器放置向導不會強制用戶選擇輸出格式,建議使用差分輸出,因為這些擺幅較低信令格式具有固有的平衡性,因此可以最大程度地減少共模噪聲的產生.共模噪聲通常是降低抖動性能和串擾的關鍵因素.相反CMOS輸出振蕩器是單端,擺幅軌到軌和具有亞皮秒的邊緣速率.由于這些因素,CMOS輸出振蕩器會在以下情況下產生明顯的單端電流浪涌:所有時鐘晶體振蕩器,因此會產生很大的串擾.由于這些原因,應在任何時候避免使用CMOS輸出尋求低抖動性能時可能實現.如果必須在頻率計劃中使用CMOS輸出,則最好放置此輸出盡可能遠離其他時鐘,中間使用未使用的輸出.輸出格式可以輕松地在Clock Builder Pro配置向導.

1.2小心放置時鐘銷

Clock Placement Wizard(時鐘晶體振蕩器放置向導)將分析所有晶體振蕩器輸出,并安排它們,以避免放置會引起抖動的晶振,集成帶寬彼此相鄰.常用的集成帶寬是12kHz至20MHz. ClockPlacement向導在其算法中使用此帶寬.如果兩個有源晶振,晶體振蕩器輸出之間的間隔接近20MHz輸出頻率,這可能會導致串擾問題.

例如,如果振蕩器2為155.52MHz,振蕩器3為156.25MHz,則156.25MHz–155.52MHz=730kHz.由于730kHz在12kHz至20MHz的集成帶寬內,因此CPW的自動放置算法假設有更好的選擇,我們嘗試找到一種避免將這兩個振蕩器相互放置的方法.這兩個輸出信號將如果并排放置,則會在730kHz和730kHz的倍數處產生雜散,這些雜散將在12kHz至20MHz的積分頻帶內.這些雜散會導致更高的抖動.如果有未使用的時鐘輸出,最好在兩個晶體振蕩器之間有一個未使用的時鐘輸出在此示例中,晶振2和晶振3.此外,晶振2和晶振3應該與其他更高頻率放置在更遠的地方它們之間的差距要大得多,并且超出了集成范圍.

請注意,積分帶寬接近度放置算法不適用于彼此簡單整數倍的晶體振蕩器.例如,即使10MHzx2=20MHz和20MHz,也可以將20MHz振蕩器和10MHz振蕩器彼此并排放置.MHz–10MHz=10MHz,兩者都位于積分頻帶內.簡單整數關系不是問題的原因這是因為一個時鐘的邊沿不相對于另一時鐘的邊沿移動.時鐘放置向導將全部考慮在內.

1.3考慮降低輸出擺幅和I/O電壓

如果使用時鐘晶體振蕩器放置向導無法獲得最佳性能,并且您的設計中包含了AN862手動引腳放置的詳細信息,則可以通過使用較低的I/O電壓(2.5或1.8V)來改善差分晶振,晶體振蕩器抖動性能.用于CMOS和/或定制的低擺幅差分輸出信號設置.

2.使用時鐘晶體振蕩器放置向導在“定義輸出頻率”菜單步驟中訪問“時鐘放置向導”,如下所示.請注意,此示例頻率計劃的某些輸出旁邊當前有警告符號.這些警告表明輸出位置尚未針對抖動和串擾進行優化.

圖2.1.定義的輸出頻率,訪問時鐘晶體振蕩器放置向導

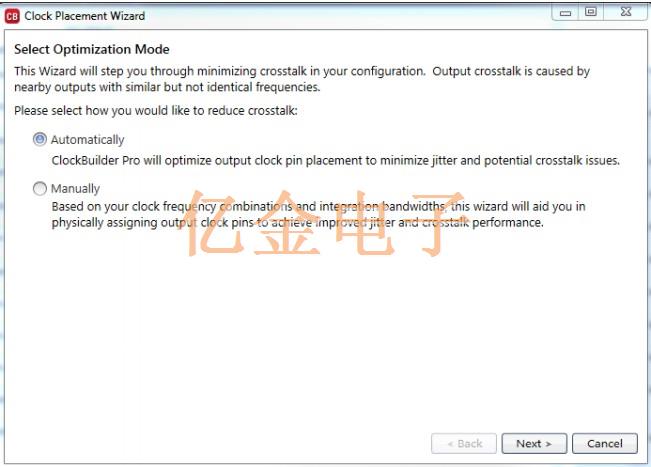

單擊“時鐘放置向導”按鈕,出現兩個選項:

1.自動優化輸出時鐘放置,以運行自動放置算法.

2.手動優化輸出時鐘位置,從而可以快速重新排列輸出順序.

圖2.2.選擇時鐘晶體振蕩器放置的優化模式

3.結論

通過遵循本應用筆記中描述的準則,并使用時鐘晶體振蕩器放置向導,可以快速輕松地實現Si534x/8x系列抖動振蕩器和時鐘晶體振蕩器的最佳抖動和串擾性能.

全球咨詢熱線

全球咨詢熱線 手機端

手機端

億金公眾號

億金公眾號 億金微信號

億金微信號