這樣設(shè)計(jì)PCB中晶振電路減少問題

不管是產(chǎn)品選型,還是電路設(shè)計(jì),對(duì)于工程而言總會(huì)遇到大大小小的問題,那么如何更好的設(shè)計(jì)PCB呢?這樣設(shè)計(jì)PCB印刷電路板減少問題,在設(shè)計(jì)印刷電路板時(shí),應(yīng)考慮通過防止來抑制EMI水平負(fù)阻力下降.

1.PCB上的圖案長(zhǎng)度

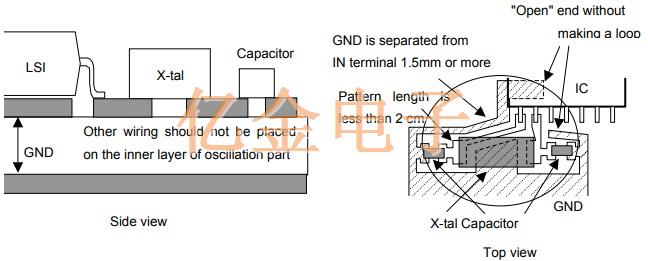

為了防止布線的電感和雜散電容導(dǎo)致電氣特性的劣化,建議以最短的接線長(zhǎng)度連接IC和電容器的石英晶體單元.這種模式長(zhǎng)度應(yīng)大約在2厘米以內(nèi),但長(zhǎng)度越短,EMI輻射越小放置IC和晶體單元等元件不會(huì)成為問題.由于EMI主要來自于在逆變器的OUT側(cè),該部分的圖形長(zhǎng)度應(yīng)該是晶體振蕩電路中最短的.而且,插件晶振不是優(yōu)選的,因?yàn)樗鼈兂蔀镋MI的來源.

2.晶體振蕩電路以外的圖案的影響

在設(shè)計(jì)多層PCB的情況下,重要的是不設(shè)計(jì)場(chǎng)地或其他信號(hào)模式在圖中圓圈部分的振蕩電路下,以防止負(fù)電阻減小,并獲得石英晶體振蕩器穩(wěn)定的啟動(dòng)特性.特別是,如果其他信號(hào)線位于靠近IN側(cè)的位置振蕩電路,振蕩波形將被調(diào)制引起噪聲,并在OUT側(cè)放大成為EMI的原因.由于晶體振蕩電路可能會(huì)停止啟動(dòng),如果IN端子的電壓和OUT端子在其他信號(hào)線的影響下變得相等,強(qiáng)烈建議不要設(shè)計(jì)它.還應(yīng)該避免在振蕩電路附近的層上放置場(chǎng)地,因?yàn)樗鼤?huì)減少負(fù)面阻力很大.

3.用場(chǎng)地屏蔽

當(dāng)用場(chǎng)地屏蔽時(shí),它將被放置在距離元件側(cè)最遠(yuǎn)的層上,如圖所示左下圖.接地圖案不應(yīng)放置在有源晶振,晶體振蕩電路中以避免負(fù)電阻降低,并且其他信號(hào)線也不應(yīng)該放在這個(gè)部分,因?yàn)樗鼤?huì)調(diào)制振蕩波形和通過降低負(fù)電阻來增加EMI.

如果元件上的有源晶振振蕩電路的接地圖案一側(cè)靠近信號(hào)線放置,EMI水平會(huì)降低,但如果放得太近,它會(huì)減少負(fù)阻,建議將其與振蕩電路的信號(hào)線分開0.5mm或更多.將接地圖案設(shè)置得太靠近振蕩電路的信號(hào)線是不利的,會(huì)降低負(fù)電阻,此外由于從IN輻射的EMI水平低,沒有必要這樣做.

“推薦閱讀”

【責(zé)任編輯】:億金電子版權(quán)所有:http://www.bzmfr.cn轉(zhuǎn)載請(qǐng)注明出處

相關(guān)行業(yè)新聞

- KDS晶振開發(fā)了世界上最小的TCXO振蕩器

- 泰藝電子1.2V低功耗溫補(bǔ)晶振TZ-L系列

- ABM8AAIG晶體是2焊盤的車規(guī)級(jí)陶瓷晶體

- KX-ZTT溫度范圍更大的陶瓷諧振器

- Abracon向電子市場(chǎng)推出多個(gè)創(chuàng)新MEMS振蕩器系列

- SiTime計(jì)時(shí)的故事:硅MEMS振蕩器

- 用于小型可穿戴設(shè)備的村田晶體諧振器

- 使用HCMOS振蕩器的源阻抗端接建議

- HCMOS晶體振蕩器面臨的挑戰(zhàn)

- UC XO 系列用于PCIe網(wǎng)絡(luò)和計(jì)算應(yīng)用

全球咨詢熱線

全球咨詢熱線 手機(jī)端

手機(jī)端

億金公眾號(hào)

億金公眾號(hào) 億金微信號(hào)

億金微信號(hào)